CORDIC Calculator with JTAG

16-bit fixed point implementation in VHDL for FPGA, pipelined for 20x speed-up, JTAG interface

Project code available here: https://github.com/garrettknuf/CORDIC-Calculator

Overview

In this project, I implemented a 16-bit fixed-point CORDIC (COordinate Rotation DIgital Computer) algorithm in VHDL for FPGA-based trigonometric and hyperbolic computations. The design features a configurable pipelined architecture, capable of achieving a 20x speed-up compared to a fully parallel architecture. Additionally, the system includes a JTAG interface, enabling seamless debugging and interaction with an FPGA development board.

Why CORDIC?

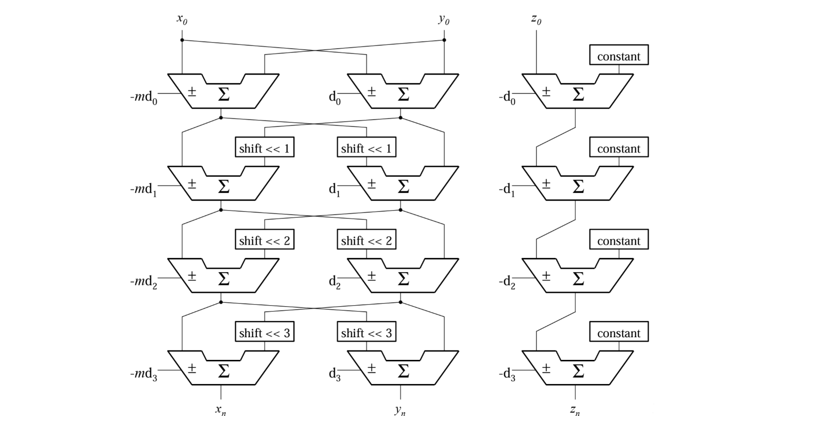

CORDIC is an efficient, hardware-friendly algorithm for computing trigonometric, hyperbolic, and logarithmic functions using only shift and add operations—eliminating the need for costly multipliers. This makes it well-suited for FPGA implementations, particularly in embedded signal processing, communications, and real-time control applications.

Implementation Details

16-bit Fixed-Point Representation

The input and output data use a signed 16-bit fixed-point format. The format follows Q1.14 representation (1 sign bit, 1 integer bit, 14 fractional bits), offering a balance between precision and hardware complexity, though the signed computation functionality was not implemented for this design.

Pipelined Architecture

The implementation employs a fully unrolled pipeline with a configurable number of stages. Each stage performs a single shift-and-add iteration. After synthesis, the pipelined design achieved a 20x throughput improvement compared to a basic parallel approach.

JTAG Interface for Debugging and Control

A JTAG interface is integrated to allow interaction between the FPGA and standard JTAG tools, enabling real-time coefficient updates and debugging without requiring FPGA reprogramming.