Delay-Locked Loop

8 GHz, 15% jitter, 4% DCD, 6 mW, 45nm (schematic) with phase detector, charge pump, and delay-line

8 GHz, 15% jitter, 4% DCD, 6 mW, 45nm (schematic) with phase detector, charge pump, and delay-line

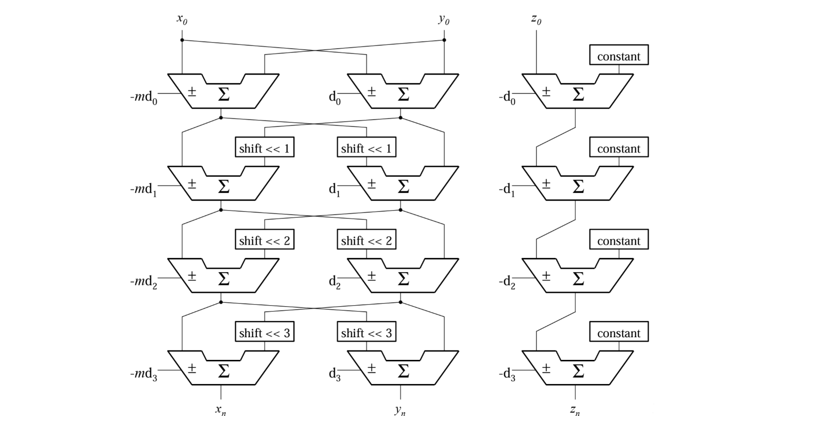

16-bit fixed point implementation in VHDL for FPGA, pipelined for 20x speed-up, JTAG interface

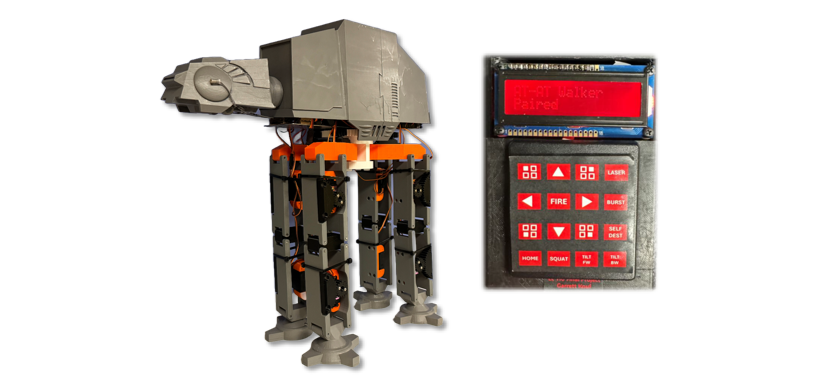

12-DOF robot, PCB Design for 4-device BLE-network, ARM Assembly, TI RTOS in C

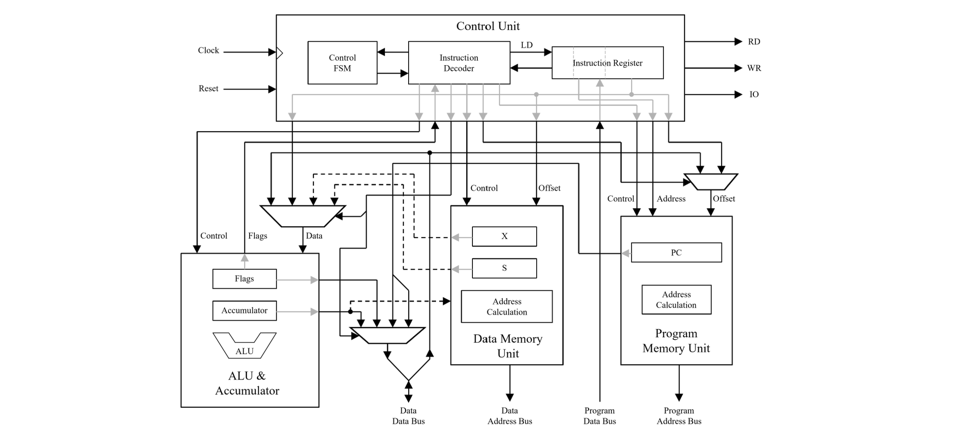

Implementation of 8-bit Harvard Architecture, accumulator-based CPU. The CPU has an 8-bit accumulator, two 8-bit data addressing registers (X and S) and a 13-bit program counter. All instruction ar...

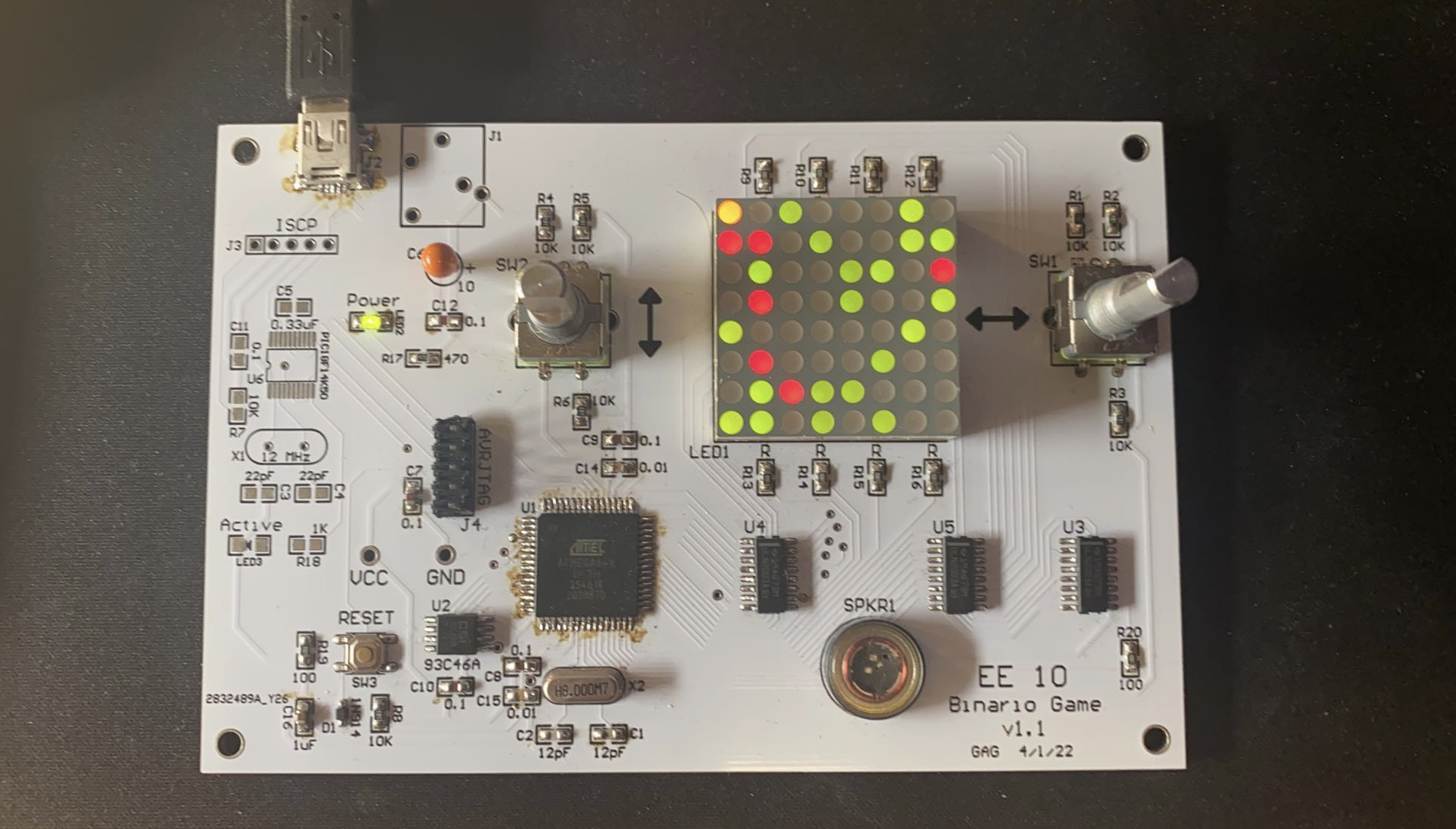

MCU programmed in AVR assembly to run an interactive Binario game. Features on this board include a multiplexed 8x8 LED matrix, debounced switches and encoders, tone generation, and EEROM.

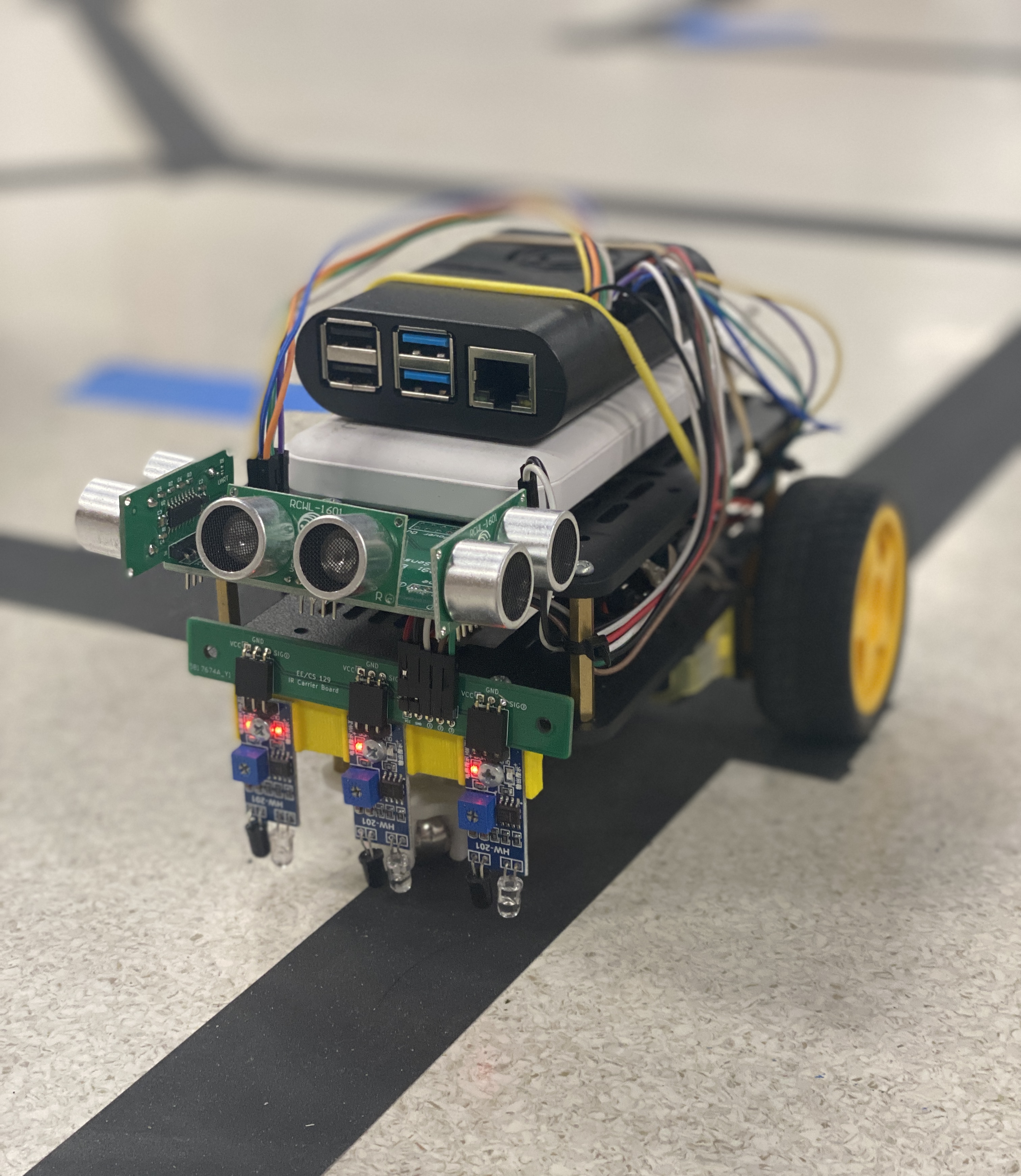

2 wheeled autonomous rover that explores maps with IR sensors, ultrasound detectors, and advanced maze-navigating algorithms and decision making processes.